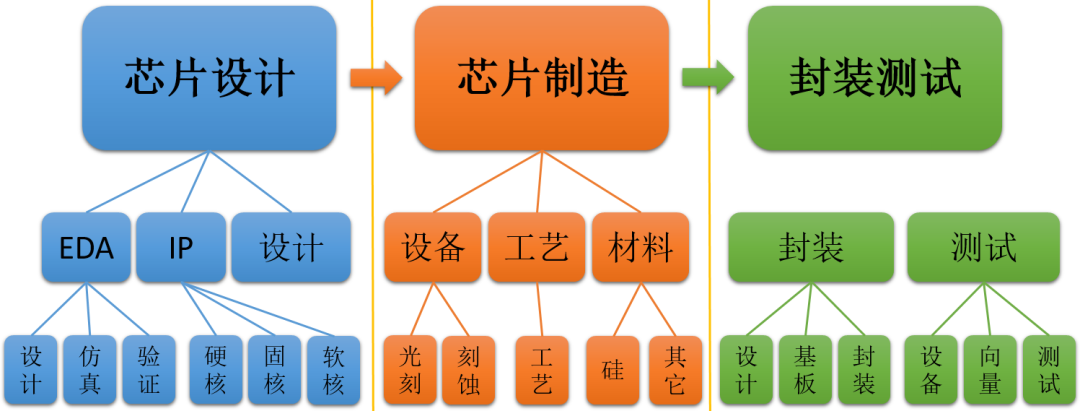

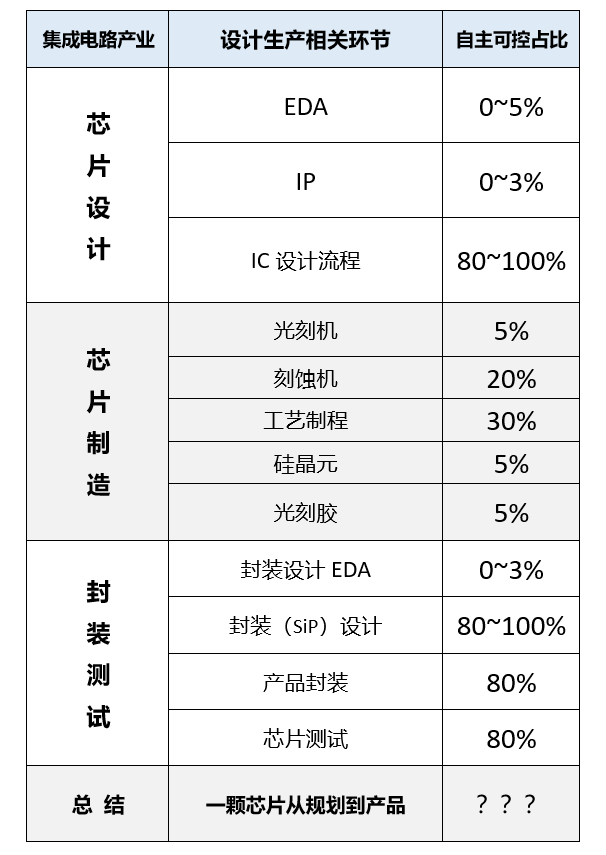

集成电路产业通常被分为芯片设计、芯片制造、封装测试三大领域,参看下图:

1.2 IP

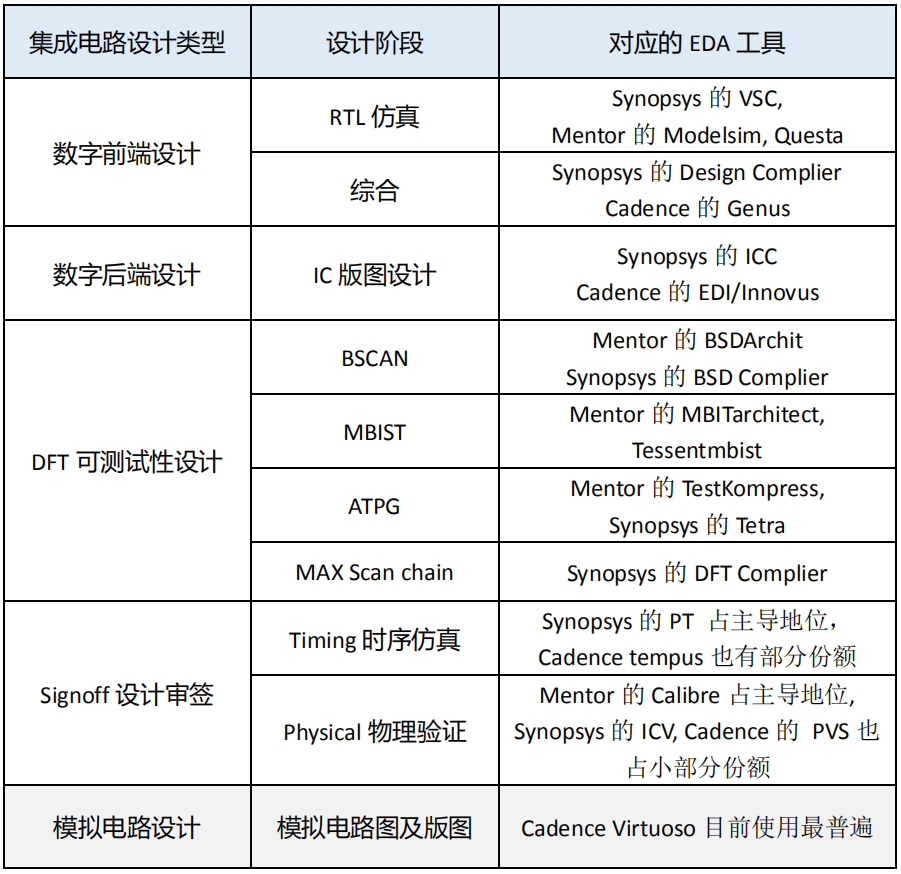

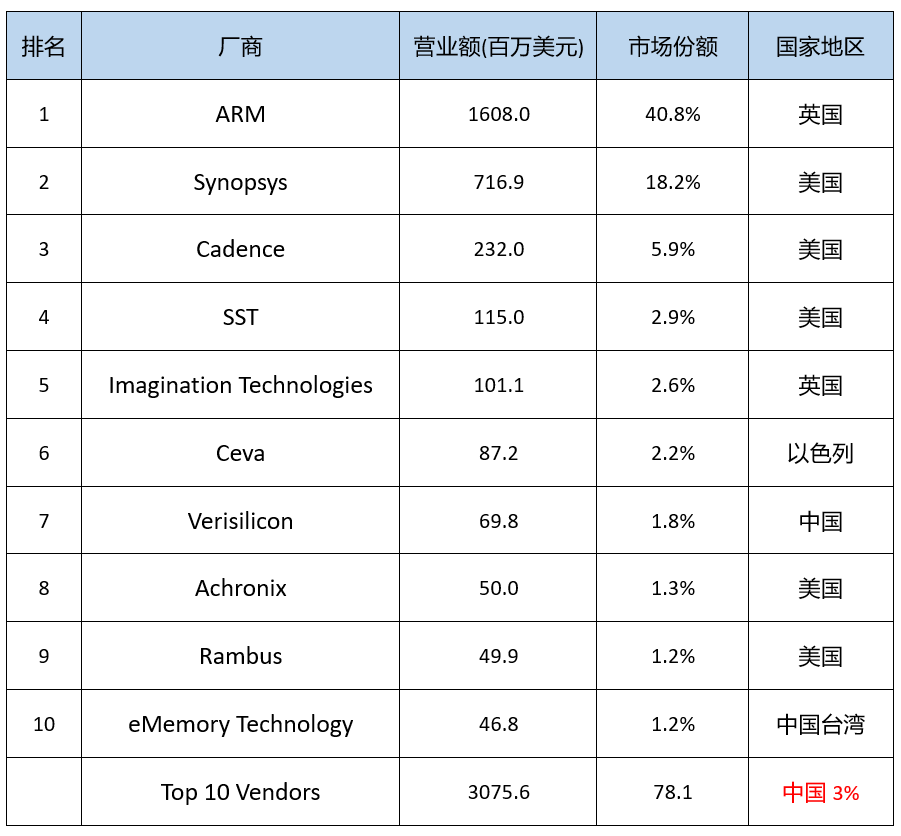

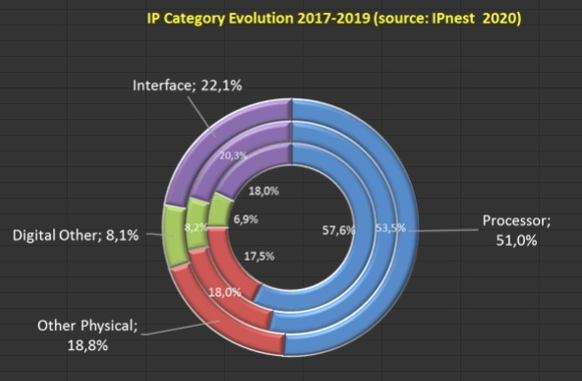

下表为目前全球前10大IP提供商,可以看到中国有两家入围前十,但是两家市场份额加起来也仅有3%,而ARM一家就占据了40%以上的市场份额,美国的企业则占据了30%的市场份额,如果ARM被英伟达收购,基本上IP市场就是美国的天下了。此外我们也发现,全球最大的两家EDA公司Synopsys和Cadence,在IP领域也同样占据的第二、第三的位置。

下图所示为IP的种类,其中处理器占51%,接口IP占22.1%,数字类占8.1%,其他占18.8%,处理器类ARM一家独大,在接口类IP中,Synopsys是业界领导者。

我们需要考虑的是,在设计的芯片中那些IP是自主设计的,那些是外购的,这些外购的IP是否存在不可控因素?如果你设计的SoC仅仅是把别人的IP打包整合,那自主可控性就要大打折扣了。

下面,我们以华为麒麟980为例,了解一下芯片研发中的IP使用情况。

麒麟980芯片集成的主要部件有CPU、GPU(俗称显卡)、ISP(处理拍照数据)、NPU(人工智能引擎)和基带(负责通信)。

根据华为官方资料,ISP是华为自研,NPU是华为和寒武纪合作的成果,至于CPU(Cortex-A76)和GPU(Mali-G76)则是华为向ARM公司购买的授权,包括指令集授权和内核授权。

如果没有IP授权,还有没有可能自研麒麟980芯片,目前看来,没有 。

1.3 设计流程

芯片设计流程通常可分为:数字IC设计流程和模拟IC设计流程。

数字IC设计流程:芯片定义 → 逻辑设计 → 逻辑综合 → 物理设计 → 物理验证 → 版图交付。

芯片定义(Specification)是指根据需求制定芯片的功能和性能指标,完成设计规格文档。

逻辑设计(Logic Design)是指基于硬件描述语言在RTL(Register-Transfer Level)级实现逻辑设计,并通过逻辑验证或者形式验证等验证功能正确。

逻辑综合(Logic Synthesis)是指将RTL转换成特定目标的门级网表,并优化网表延时、面积和功耗。

物理设计(Physical Design)是指将门级网表根据约束布局、布线并最终生成版图的过程,其中又包含:数据导入 → 布局规划 → 单元布局 → 时钟树综合 → 布线。

数据导入是指导入综合后的网表和时序约束的脚本文件,以及代工厂提供的库文件。

布局规划是指在芯片上规划输入/输出单元,宏单元及其他主要模块位置的过程。

单元布局是根据网表和时序约束自动放置标准单元的过程。

时钟树综合是指插入时钟缓冲器,生成时钟网络,最小化时钟延迟和偏差的过程。

布线是指在满足布线层数限制,线宽、线间距等约束条件下,根据电路关系自动连接各个单元的过程。

物理验证(Physical Verificaiton)通常包括版图设计规则检查(DRC),版图原理图一致性检查(LVS)和电气规则检查(ERC)等。

版图交付(Tape Out)是在所有检查和验证都正确无误的前提下,传递版图文件给代工厂生成掩膜图形,并生产芯片。

模拟IC设计流程:芯片定义 → 电路设计 → 版图设计 → 版图验证 → 版图交付。

其中芯片定义和版图交付和数字电路相同,模拟IC在电路设计、版图设计、版图验证和数字电路有所不同。

模拟电路设计是指根据系统需求,设计晶体管级的模拟电路结构,并采用SPICE等仿真工具验证电路的功能和性能。

模拟版图设计是按照设计规则,绘制电路图对应的版图几何图形,并仿真版图的功能和性能。

模拟版图验证是验证版图的工艺规则、电气规则以及版图电路图一致性检查等。

这里,我们做一个简单的总结:

芯片设计:就是在EDA工具的支持下,通过购买IP授权+自主研发(合作开发)的IP,并遵循严格的集成电路设计仿真验证流程,完成芯片设计的整个过程。在这个过程中,EDA、IP、严格的设计流程三者缺一不可。

目前看来,在这三要素中最先可能实现自主可控的就是设计流程了。

下表列出了当前世界前10的芯片设计公司,供大家参考。

02

芯 片 制 造

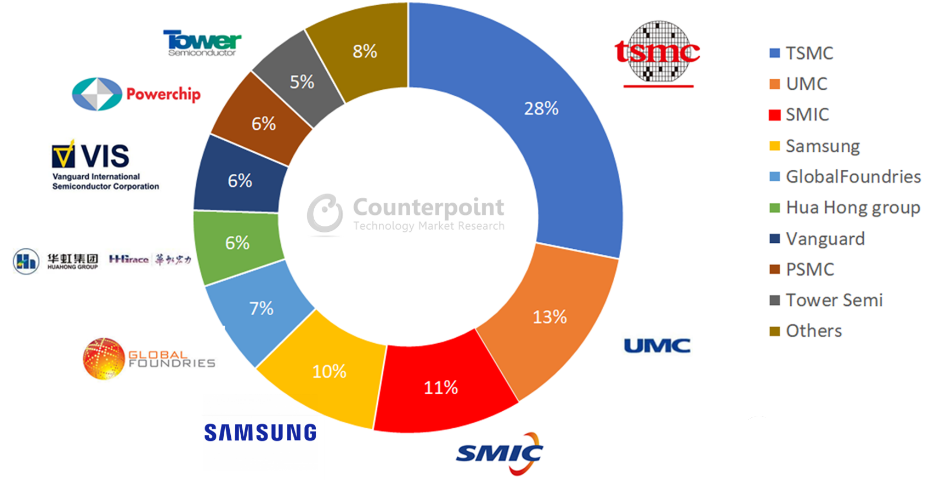

芯片制造目前是集成电路产业门槛最高的行业,怎么看待门槛的高低呢,投资越高、玩家越少就表明门槛越高,目前在高端芯片的制造上也仅剩下台积电(TSMC)、三星(SAMSUNG)和英特尔(Intel)三家了。

下面,我们分别从设备、工艺和材料三个方面来分析芯片制造,寻找我们和先进制造技术的差距。

2.1 设备

芯片制造需要经过两千多道工艺制程才能完成,每个步骤都要依赖特定设备才能实现。

芯片制造中,有三大关键工序:光刻、刻蚀、沉积。三大工序在生产过程中不断重复循环,最终制造出合格的芯片。

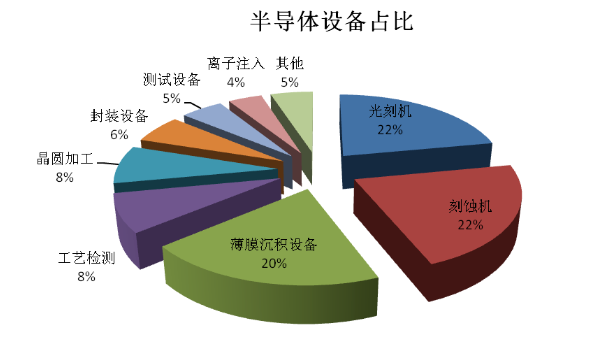

三大关键工序要用到三种关键设备,分别是光刻机、刻蚀机、薄膜沉积设备。三大设备占所有设备投入的22%、22%、20%左右,是三种占比最高的半导体设备。

下面就以最为典型的光刻机和刻蚀机为例进行介绍并分析自主可控。

光刻机

光刻机的原理其实像幻灯机一样,就是把光通过带电路图的掩膜(也叫光罩)Mask投影到涂有光刻胶的晶圆上。60年代末,日本尼康和佳能开始进入这个领域,当时的光刻机并不比照相机复杂多少。

刻蚀机

刻蚀是将晶圆表面不必要的材质去除的过程。刻蚀工艺位于光刻之后。

光刻机用光将掩膜上的电路结构复制到硅片上,刻蚀机把复制到硅片上的电路结构进行微雕,雕刻出沟槽和接触点,让线路能够放进去。

按照刻蚀工艺分为干法刻蚀以及湿法刻蚀,干法刻蚀主要利用反应气体与等离子体进行刻蚀,湿法刻蚀工艺主要是将刻蚀材料浸泡在腐蚀液内进行刻蚀。

干法刻蚀在半导体刻蚀中占据主流,市场占比达到95%,其最大优势在于能够实现各向异性刻蚀,即刻蚀时可控制仅垂直方向的材料被刻蚀,而不影响横向材料,从而保证细小图形保真性。湿法刻蚀由于刻蚀方向的不可控性,在先进制程很容易降低线宽,甚至破坏线路本身,导致芯片品质变差。

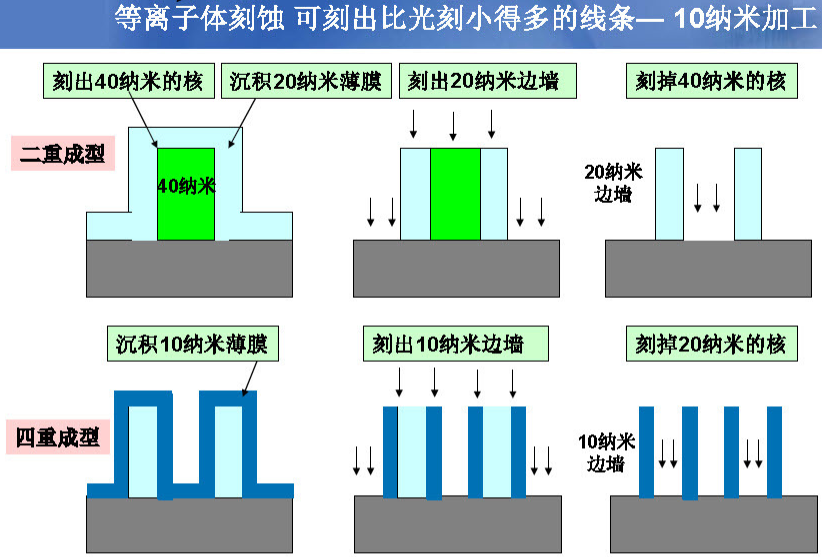

目前普遍采用多重模板工艺原理,即通过多次沉积、刻蚀工艺实现需要的特征尺寸,例如14nm制程所需使用的刻蚀步骤达到64次,较 28nm提升60%;7nm制程所需刻蚀步骤更是高达140次,较14nm提升118%。

下图所示为多次刻蚀原理。

和光刻机一样,刻蚀机的厂商也相对较少,代表企业主要是美国的 Lam Research(泛林半导体)、AMAT(应用材料)、日本的TEL(东京电子)等企业。这三家企业占据全球半导体刻蚀机的94%的市场份额,而其他参与者合计仅占6%。其中,Lam Research 占比高达55%,为行业龙头,东京电子与应用材料分别占比20%和19%。

国内的情况,目前刻蚀设备代表公司为中微公司、北方华创等。中微公司较为领先,工艺节点已经达到5nm。在全球前十大晶圆企业中,中微公司已经进入其中六家,作为台积电的合作伙伴协同验证14nm/7nm/5nm等先进工艺。

基于此,如果目前在光刻机领域我们还无力做出改变,那么已经有一定优势的刻蚀机势必会成为国产替代的先锋。

2.2 工艺制程

芯片制造过程需要两千多道工艺制程,下面,我们按照8大步骤对芯片制造工艺进行简单介绍。

1. 光刻(光学显影)

光刻是经过曝光和显影程序,把光罩上的图形转换到光刻胶下面的晶圆上。光刻主要包含感光胶涂布、烘烤、光罩对准、 曝光和显影等程序。曝光方式包括:紫外线、极紫外光、X射线、电子束等。

2. 刻蚀(蚀刻)

刻蚀是将材料使用化学反应或物理撞击作用而移除的技术。干刻蚀(dry etching)利用等离子体撞击晶片表面所产生的物理作用,或等离子体与晶片表面原子间的化学反应,或者两者的复合作用。湿刻蚀(wet etching)使用的是化学溶液,经过化学反应达到刻蚀的目的。

3. 化学气相沉积(CVD)

CVD利用热能、放电或紫外光照射等化学反应的方式,将反应物在晶圆表面沉积形成稳定固态薄膜(film)的一种沉积技术。CVD技术在芯片制程中运用极为广泛,如介电材料(dielectrics)、导体或半导体等材料都能用CVD技术完成。

4. 物理气相沉积(PVD)

PVD是物理制程而非化学制程,一般使用氩等气体,在真空中将氩离子加速以撞击溅镀靶材后,可将靶材原子一个个溅击出来,并使被溅击出来的材质如雪片般沉积在晶圆表面。

5. 离子植入(Ion Implant)

离子植入可将掺杂物以离子型态植入半导体组件的特定区域上,以获得精确的电特性。离子先被加速至足够能量与速度,以穿透(植入)薄膜,到达预定的植入深度。离子植入可对植入区内的掺质浓度加以精密控制。

6. 化学机械研磨(CMP)

化学机械研磨技术具有研磨性物质的机械式研磨与酸碱溶液的化学式研磨两种作用,可以使晶圆表面达到全面性的平坦化,以利后续薄膜沉积。

7. 清洗

清洗的目的是去除金属杂质、有机物污染、微尘与自然氧化物;降低表面粗糙度;几乎所有制程前后都需要清洗。

8. 晶片切割(Die Saw)

晶片切割是将加工完成的晶圆上一颗颗晶粒裸芯片(die)切割分离,便于后续封装测试

2.3 材料

03

封 装 测 试

3.1 芯片封装

我们从封装设计和产品封装两方面来分析芯片封装。

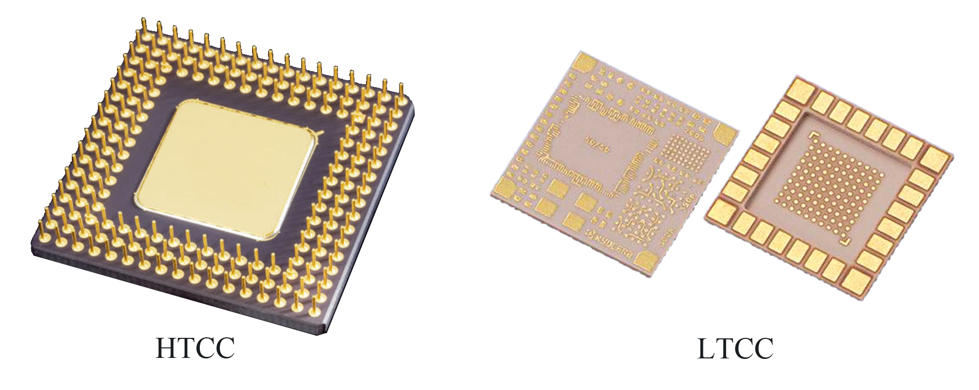

早先的封装中没有集成(Integration)的概念,封装设计是比较简单的,对工具要求也很低,Auto CAD就是常用的封装设计工具,随着MCM、SiP技术的出现,封装设计变得越来越复杂,加上目前SiP、先进封装、Chiplet、异构集成概念的市场接受度越来越高,封装内集成的复杂度和灵活度急剧上升,对封装设计的要求也越来越高,

SiP和先进封装设计工具目前只有Cadence和 Siemens EDA(Mentor)两家,Cadence是老牌的封装设计EDA提供商,市场占有率高,用户的忠诚度也比较高。

Siemens EDA(Mentor)是封装设计领域的后起之秀,但其技术先进性上则体现了“后浪”的特点。业界大佬TSMC, Intel, SAMSUNG纷纷选择Siemens EDA作为其先进封装(HDAP)的首选工具,主要在于两点:先进的设计工具和强悍的验证工具。

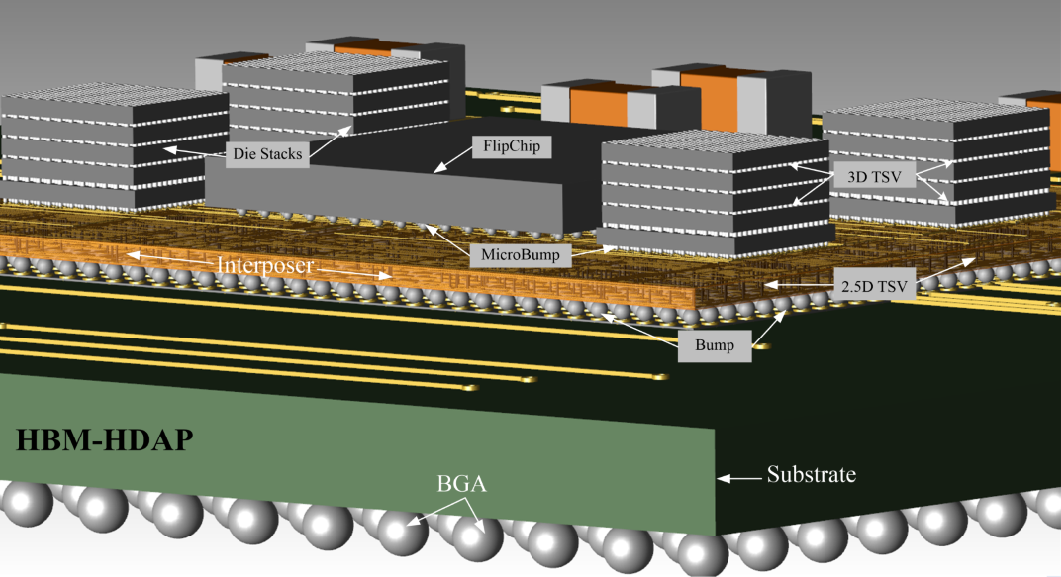

首先我们说说设计工具,在一次技术论坛中,我说:“不同于传统封装设计,先进封装和SiP设计对3D环境要求很高,3D设计环境不在于是否看上去很直观、绚丽,而在于对客观元素的精准描述,包括键合线、腔体、芯片堆叠、硅转接板、2.5D集成、3D集成,Bump...”

在这一点上,Siemens EDA的SiP及先进封装设计工具已经远远将其竞争对手抛在身后。下图为先进封装版图设计工具XPD中的封装设计3D截图,4组芯片堆叠中,每组5颗芯片(4HBM+1Logic)以3D TSV连接在一起,和GPU一起集成在硅转接板(2.5D TSV)上,硅转接板和电阻、电容等一起集成在封装基板上。

XPD中的先进封装设计截图(3D)

3.2 芯片测试

机台测试

测试向量可基于EDA工具的仿真向量(包含输入信号和期望的输出),经过优化和转换,形成ATE格式的测试向量。利用EDA工具建立器件模型,通过建立一个Testbench仿真验证平台,对其提供测试激励,进行仿真,验证结果,将输入激励和输出响应存储,按照ATE向量格式,生成ATE向量文件。

系统测试

自主可控总结

TPOWER天源中芯代理商|winbond华邦代理商|3peak思瑞浦代理商|INJOINIC英集芯代理商|EON宜扬代理商|MAXIM美信代理商|Holtek合泰代理商|Xilinx赛灵思代理商|Microchip微芯代理商|MPS芯源代理商|模拟IC|国产MCU|电源芯片|IC代理商|IC供应商|深圳IC|IC代理|一级代理商-找昊海鑫科技(微信/电话:18676367856 QQ:1289315967 陈功)

首页产品中心代理品牌IC学院 IC资讯成功案例常见问题了解昊海鑫 企业新闻联系我们企业招聘

Copyright © 2005-2010 All rights reserved 深圳市昊海鑫科技有限公司 粤ICP备18143393号CNZZ()

地址:广东省深圳市宝安区西乡街道固戍社区宝源路北侧宝港中心411电话:0755-33561021

传真:0755-85298357邮箱:haixinkeji@163.com技术支持:昊海鑫科技

深圳最专业的IC代理商,IC供应商,TPOWER代理商,英集芯代理商,3PEAK代理商,帝奥微代理商,纳芯微代理商,EON代理商,Winbond代理商.你身边最优秀的IC供应商合作伙伴

升邦科技官方微信

扫一扫立即加关注

扫一扫立即加关注